功能说明

面向分离架构的核间同步控制接口。

该接口和CrossCoreWaitFlag接口配合使用。使用时需传入核间同步的标记ID(flagId), 每个ID对应一个初始值为0的计数器。执行CrossCoreSetFlag后ID对应的计数器增加1;执行CrossCoreWaitFlag时如果对应的计数器数值为0则阻塞不执行;如果对应的计数器大于0,则计数器减一,同时后续指令开始执行。

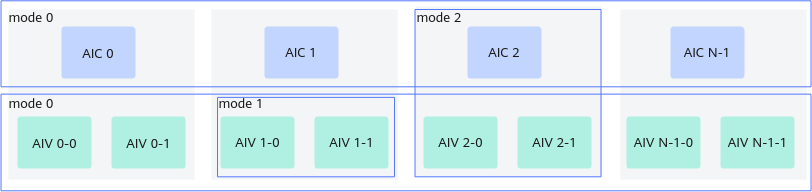

同步控制分为3种模式,如图1所示:

- 模式0:AI Core核间的同步控制。对于AIC场景,同步所有的AIC核,直到所有的AIC核都执行到CrossCoreSetFlag时,CrossCoreWaitFlag后续的指令才会执行;对于AIV场景, 同步所有的AIV核,直到所有的AIV核都执行到CrossCoreSetFlag时,CrossCoreWaitFlag后续的指令才会执行。

- 模式1:AI Core内部,AIV核之间的同步控制。如果两个AIV核都运行了CrossCoreSetFlag,CrossCoreWaitFlag后续的指令才会执行。

- 模式2:AI Core内部,AIC与AIV之间的同步控制。在AIC核执行CrossCoreSetFlag之后, 两个AIV上CrossCoreWaitFlag后续的指令才会继续执行;两个AIV都执行CrossCoreSetFlag后,AIC上CrossCoreWaitFlag后续的指令才能执行。

函数原型

1 2 | template <uint8_t modeId, pipe_t pipe> __aicore__ inline void CrossCoreSetFlag(uint16_t flagId) |

参数说明

参数名 |

描述 |

|---|---|

modeId |

核间同步的模式,取值范围为0~2。

|

pipe |

设置这条指令所在的流水类型,不支持PIPE_S和PIPE_ALL。 流水类型可参考表1。 |

参数名 |

输入/输出 |

描述 |

|---|---|---|

flagId |

输入 |

核间同步的标记,取值范围是0-10。 |

返回值

无

支持的型号

Atlas A2训练系列产品/Atlas 800I A2推理产品

约束说明

- 因为Matmul高阶API内部实现中使用了本接口进行核间同步控制,所以不建议开发者同时使用该接口和Matmul高阶API,否则会有flagID冲突的风险。

- 同一flagId的计数器最多设置16次。

调用示例

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 | // 使用模式0的方式同步所有的AIV核 if (g_coreType == AscendC::AIV) { AscendC::CrossCoreSetFlag<0x0, PIPE_MTE3>(0x8); AscendC::CrossCoreWaitFlag(0x8); } // 使用模式1的方式同步当前AICore内的所有AIV子核 if (g_coreType == AscendC::AIV) { AscendC::CrossCoreSetFlag<0x1, PIPE_MTE3>(0x8); AscendC::CrossCoreWaitFlag(0x8); } // 注意:如果调用高阶API,无需开发者处理AIC和AIV的同步 // AIC侧做完Matmul计算后通知AIV进行后处理 if (g_coreType == AscendC::AIC) { // Matmul处理 AscendC::CrossCoreSetFlag<0x2, PIPE_FIX>(0x8); } // AIV侧等待AIC Set消息, 进行Vector后处理 if (g_coreType == AscendC::AIV) { AscendC::CrossCoreWaitFlag(0x8); // Vector后处理 } |