基本原理

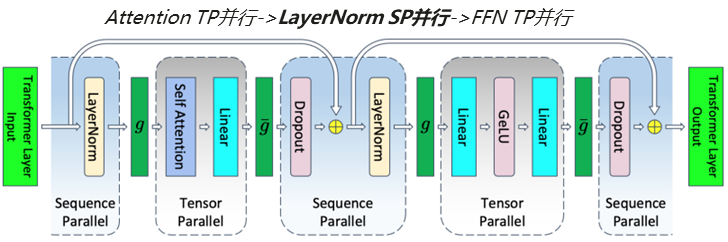

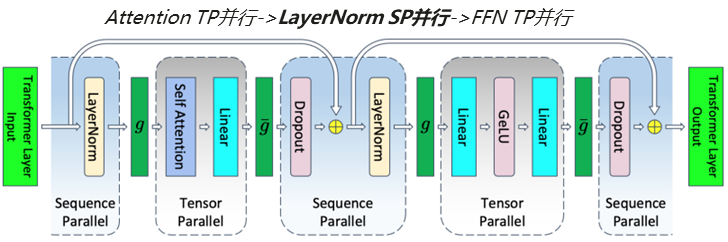

在TP并行的基础上,Transformer的 LayerNorm/Dropout部分未展开并行,存在计算及内存冗余,尤其在长序列场景,对性能影响更大。

Sequence Parallelism主要从Sequence维度进行划分,在TP并行的基础上,将Transformer的LayerNorm/Dropout层输入按Sequence Length维度进行了切分,使得各Device并行执行部分LayerNorm/Dropout计算,达到计算资源的缩减及Activation显存的占用。

图1 序列并行流程

使用场景

使用TP并行场景,当前在Atlas A2 训练系列产品上验证:LLaMA-16B单机性能提升10%,内存降低8.7%;LLaMA-32B双机性能提升9%,内存缩减6.6%;BLOOM-7B单机性能提升13.89%,内存缩减13.5%;BLOOM-176B 12节点性能提升12.02%,内存缩减3.2%。

操作步骤

使用AscendSpeed,在TP并行的基础上添加 --sequence-parallel标志。